Groningen2011 project

From 2011.igem.org

(Created page with "<!--- The Mission, Experiments ---> <div style="width: 80%; color: #cc0000; margin: auto; text-align: center"> File:RUGlogo.png <span style="font-size: 1.5em">iGEM 2011 Gro...") |

|||

| Line 16: | Line 16: | ||

[[File:Scheme1.png]] | [[File:Scheme1.png]] | ||

| + | |||

| + | ''The first input triggers the first memory unit (which consists of an autoinducing loop and a jammer-based off switch) to start. The first memory unit starts triggering the first AND gate. The second input triggers the AND gate. If the first memory unit is running, this triggers the second memory unit (which also consists of an autoinducing loop and a jammer-based off switch) to start. The second module starts trigerring the second AND gate and represses the first module with the use of the jammer-based off switch. This process can be continued, if more autoinducing loops are provided. When memory release input is introduced, the system produces an output depending on which of the memory modules is running.'' | ||

</div> | </div> | ||

Revision as of 19:19, 29 April 2011

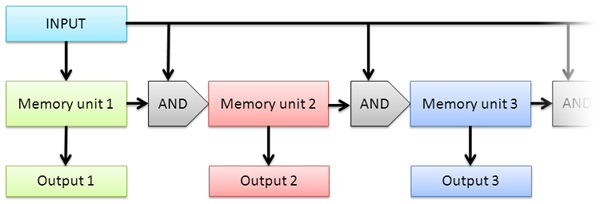

Preliminary project description

The aim of our project is to create a genetic circuit that will be able to count and memorize the occurrences of an input signal by using autoinducing loops and interfering RNA. Each increase of the counter will result in a different state of the system that will be expressed after adding a second input signal. The design of the circuit allows the system to be extended in theory infinitely.

More information will follow soon!

The first input triggers the first memory unit (which consists of an autoinducing loop and a jammer-based off switch) to start. The first memory unit starts triggering the first AND gate. The second input triggers the AND gate. If the first memory unit is running, this triggers the second memory unit (which also consists of an autoinducing loop and a jammer-based off switch) to start. The second module starts trigerring the second AND gate and represses the first module with the use of the jammer-based off switch. This process can be continued, if more autoinducing loops are provided. When memory release input is introduced, the system produces an output depending on which of the memory modules is running.

"

"